xiaowenrun

Junior Member level 3

Hello

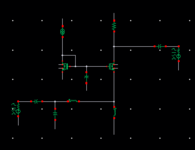

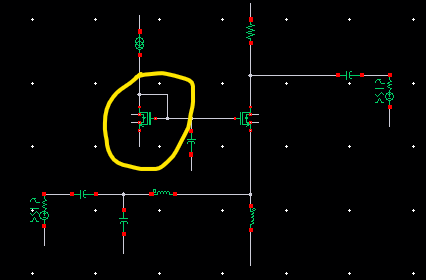

I am simulating a CG low-noise amplifier. And I found the flicker noise of the bias transistor dominates. How could it contribute more than the input transistor? The bias transistor is circled in the following picture. And how can I reduce its flicker noise?

Thanks

I am simulating a CG low-noise amplifier. And I found the flicker noise of the bias transistor dominates. How could it contribute more than the input transistor? The bias transistor is circled in the following picture. And how can I reduce its flicker noise?

Thanks