leonken

Full Member level 3

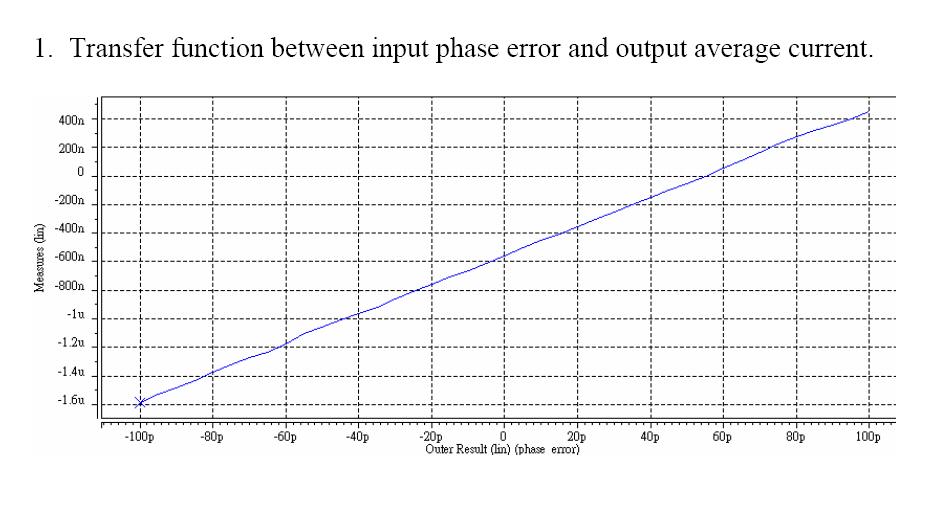

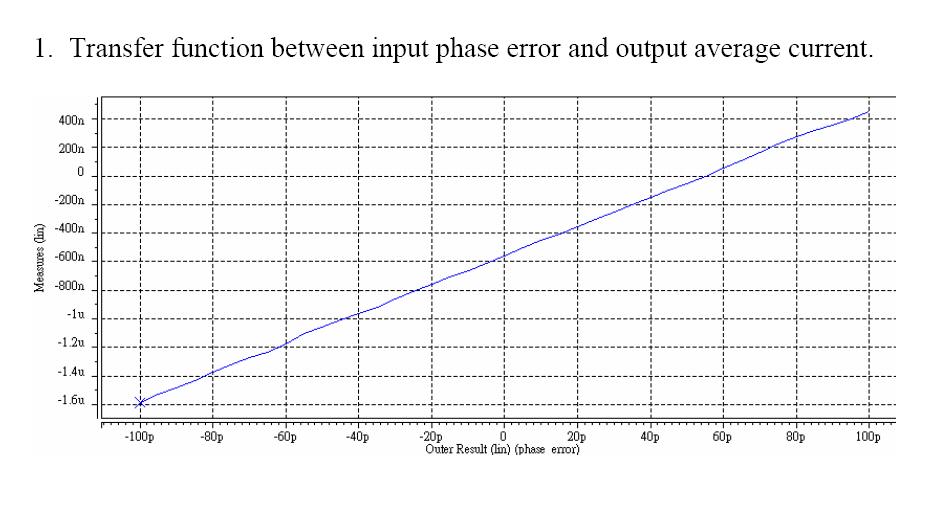

I found this figure. It is used to find out the dead zone of a PFD with CP in PLL design. The load of CP is a 1nF cap. This figure shows the dead zone vs. average current of 1nF cap.

My question is how to get the dead zone according to this figure?

Thanks.

My question is how to get the dead zone according to this figure?

Thanks.