FreshmanNewbie

Full Member level 6

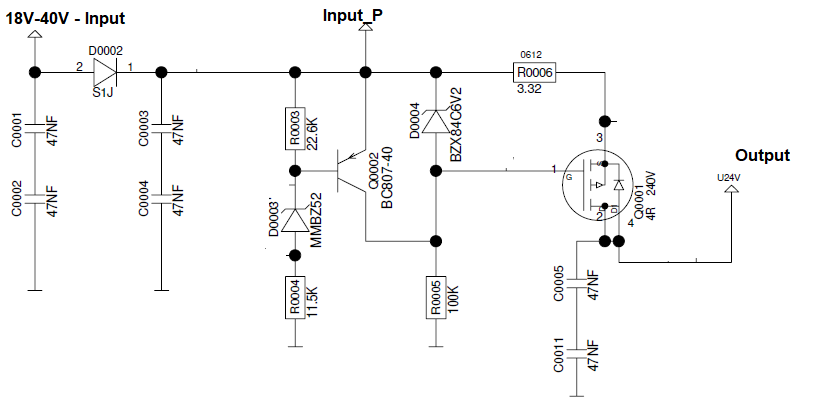

I have this circuit

I need to check whether my input capacitors C0001-c0004 are protected for ESD events.

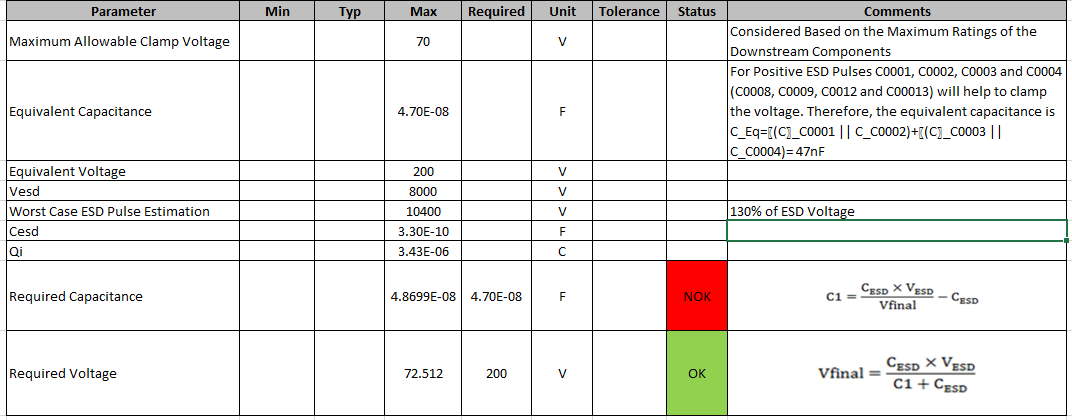

My ESD pulse spec: +/-8kV, 2kohms & 330pF. I have taken 130% of this +8kV as my ESD pulse for the worst case calculations.

I am performing the calculations as per this Article - Capacitor as ESD Protection

So, in accordance with the above article,

My calculations are below:

According to the above calculations, my questions :

I need to check whether my input capacitors C0001-c0004 are protected for ESD events.

My ESD pulse spec: +/-8kV, 2kohms & 330pF. I have taken 130% of this +8kV as my ESD pulse for the worst case calculations.

I am performing the calculations as per this Article - Capacitor as ESD Protection

So, in accordance with the above article,

My calculations are below:

According to the above calculations, my questions :

- Since the required capacitance is more than the actual capacitance present in the above calculation, does this mean, I should increase the input capacitor capacitance value? Or what does it mean?

- So, after the ESD event, the capacitors will help to clamp the voltage to 72.512V approx. , & it will be present at Input_P node and will damage the Q0002 transistor, since Q0002 Vce(max) is only 45V. Since, 72.512V > 45V, won't this 72.512 damage the transistor and the other downstream components and also components connected on the Input_P rail?

Last edited by a moderator: