desperatejobseeker

Newbie level 5

- Joined

- Mar 21, 2012

- Messages

- 10

- Helped

- 1

- Reputation

- 2

- Reaction score

- 1

- Trophy points

- 1,283

- Location

- shanghai, china

- Activity points

- 1,369

Hi all,

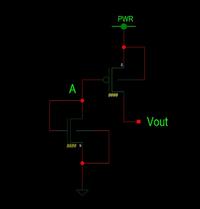

An NMOS is dioded-connected, that has its Gate/Drain tied to another PMOS gate and both its body and souce are tied to gnd. I saw many schematics using this kind of structure, I wonder how it could work? Although for the NMOS Vds>Vgs-Vth, from my perspective, there is no voltage bias at Gate/Drain, cuz they r only tied together to the gate of another PMOS. How could it possible work?

Thanks in advance!

An NMOS is dioded-connected, that has its Gate/Drain tied to another PMOS gate and both its body and souce are tied to gnd. I saw many schematics using this kind of structure, I wonder how it could work? Although for the NMOS Vds>Vgs-Vth, from my perspective, there is no voltage bias at Gate/Drain, cuz they r only tied together to the gate of another PMOS. How could it possible work?

Thanks in advance!