mtaciano

Newbie level 4

Hello,

I'm designing a 32bit CPU as a recurring assignment for my university classes. Currently it can run a single program, the next step is to make it run multiple programs preemptively, with the help of a "operating system" that would overseer the other running programs.

The problem is that it seems that my current design is very volatile, since if I make any changes it stops working. I don't know what's wrong since I'm still new to Verilog and FPGA in general, but if I could get some help making my current design better I would appreciate.

I'm using Quartus Prime 21.1.1, my target board is the Altera DE2-115.

The main things that I could pinpoint with the help of Quartus is the fact that the biggest components that where slowing down compilation where the 'Registradores.v', 'ULA.v' files and 'Mux2 mux2_mod2' component in 'CPU.v'.

The other problem is not related to compilation time, but to CPU cycles. the method I'm using for halting the program does not work, using a 'halt' input in the 'PC.v', my guess is that it's related to the CPU cycles and how an always blocks work, so I'm checking for halt not on the same clock it happens, and then the PC increments like nothing happened.

here's my CPU

the 'main' branch is the one that works, the 'dev' is the one with the changes I'm trying to make.

Here are some images i think may be important:

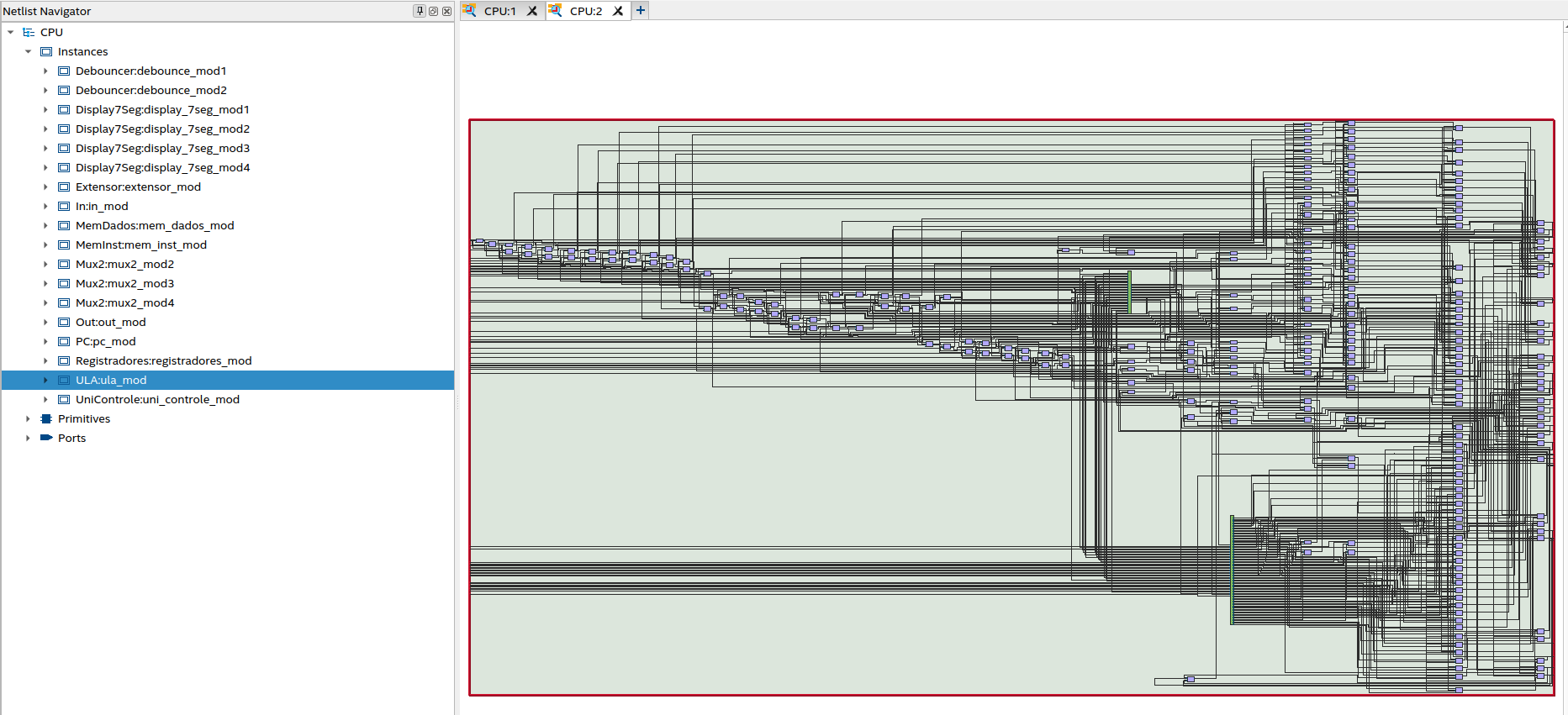

The size of ULA.v:

This one is understandable since it implements multiplication and division.

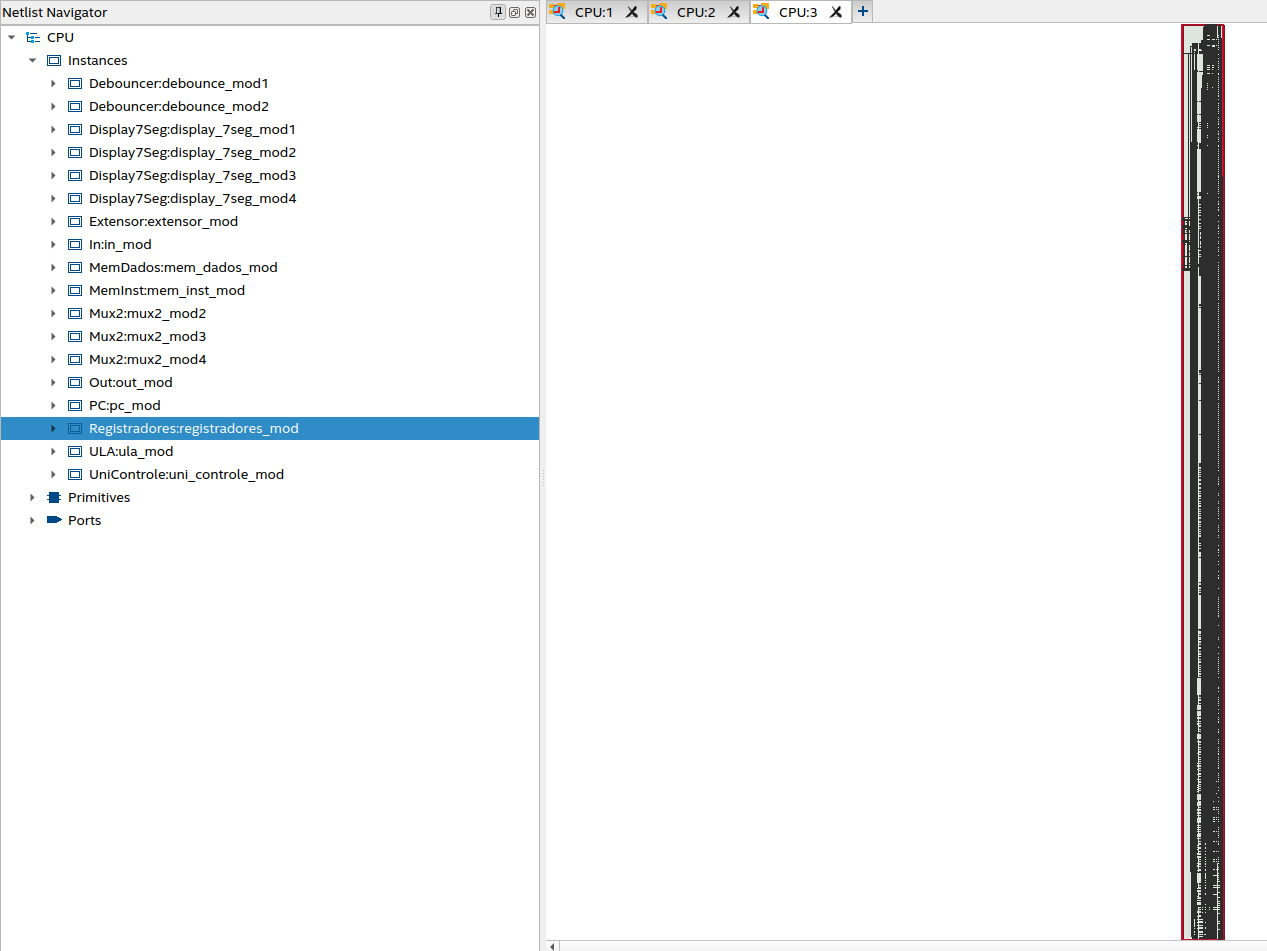

The size of Registradores.v:

This one is absolutely huge, my guess is because of the assigns but I'm clueless.

The size of Mux2 mux2_mod2:

My guess about this one is that it's because it's receiving an input from the 'Registradores.v', and that's why it's so big.

I'm designing a 32bit CPU as a recurring assignment for my university classes. Currently it can run a single program, the next step is to make it run multiple programs preemptively, with the help of a "operating system" that would overseer the other running programs.

The problem is that it seems that my current design is very volatile, since if I make any changes it stops working. I don't know what's wrong since I'm still new to Verilog and FPGA in general, but if I could get some help making my current design better I would appreciate.

I'm using Quartus Prime 21.1.1, my target board is the Altera DE2-115.

The main things that I could pinpoint with the help of Quartus is the fact that the biggest components that where slowing down compilation where the 'Registradores.v', 'ULA.v' files and 'Mux2 mux2_mod2' component in 'CPU.v'.

The other problem is not related to compilation time, but to CPU cycles. the method I'm using for halting the program does not work, using a 'halt' input in the 'PC.v', my guess is that it's related to the CPU cycles and how an always blocks work, so I'm checking for halt not on the same clock it happens, and then the PC increments like nothing happened.

here's my CPU

the 'main' branch is the one that works, the 'dev' is the one with the changes I'm trying to make.

Here are some images i think may be important:

The size of ULA.v:

This one is understandable since it implements multiplication and division.

The size of Registradores.v:

This one is absolutely huge, my guess is because of the assigns but I'm clueless.

The size of Mux2 mux2_mod2:

My guess about this one is that it's because it's receiving an input from the 'Registradores.v', and that's why it's so big.