james.qiu

Newbie level 6

Hi ,

I use FT2232HL to run a usb to spi function by python to transfer 4 bytes data. HW side , I use the channe1 and connect a level shift.

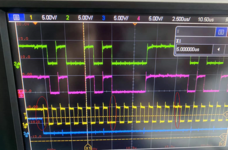

I found if i choose the data out when clk falling, and data in when clk rising , waveform is ok.

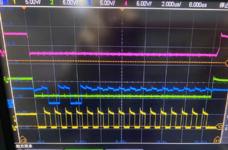

but when I try to choose another mode , data out when clk rising , and data in when clk falling , the waveform is abnormal. You can find some clk wave change the pole every 8bit data transfer. it is very strange.

I use FT2232HL to run a usb to spi function by python to transfer 4 bytes data. HW side , I use the channe1 and connect a level shift.

I found if i choose the data out when clk falling, and data in when clk rising , waveform is ok.

but when I try to choose another mode , data out when clk rising , and data in when clk falling , the waveform is abnormal. You can find some clk wave change the pole every 8bit data transfer. it is very strange.