yefj

Advanced Member level 4

Hello , I know that feedback is a time domain phenomena.

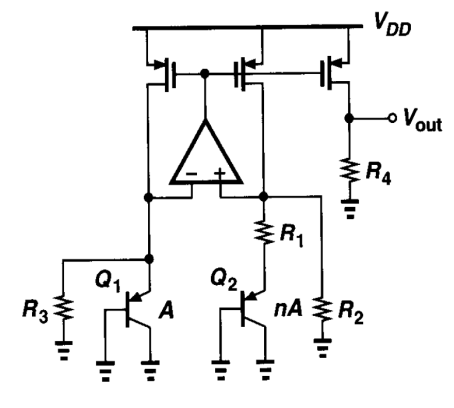

in the circuit below is there a mathematical way I could see how exactly opamp in the middle sees some "error" and tried to fix it?

Thanks.

in the circuit below is there a mathematical way I could see how exactly opamp in the middle sees some "error" and tried to fix it?

Thanks.