akbarza

Full Member level 2

hi

i tried to uplaod a pic of a circuit three times, but it was paused at 100percent . its address in gdrive is:

https://drive.google.com/file/d/1tQ5g5hVVtu5pZekBOl1jjmScpuK2WKuf/view?usp=sharing

it is only 79.1kB, So if the pic is not here, plz refer to above address.

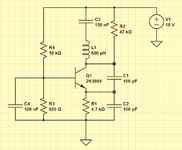

i simulate the circuit in ltspice. the circuit is a colpits oscillator. my questions areabout the circuit:

i tried to uplaod a pic of a circuit three times, but it was paused at 100percent . its address in gdrive is:

https://drive.google.com/file/d/1tQ5g5hVVtu5pZekBOl1jjmScpuK2WKuf/view?usp=sharing

it is only 79.1kB, So if the pic is not here, plz refer to above address.

i simulate the circuit in ltspice. the circuit is a colpits oscillator. my questions areabout the circuit:

- i know that for oscillation, there must be positive feedback. where is positve feedback?plz,explain

- what is roles of c3 and c4 ?

- when i saw output and i take fft of it( in ltspice) the total harmonic distortion(THD) was 18.32%. what can be done to the output be more sinosidal wave( namely, better THD)?

- when i saw output, it was a wave with amplitude between 0.7v and 18.5v. as you can see in pic the voltage source is 18 volt. is it possible and is ecceptable that the value of output is larger than power supply?