benjaminalbertmario.cella

Newbie

Hello,

I am trying to create an I2C communication between an arduino mega and an ATMEGA1284p.

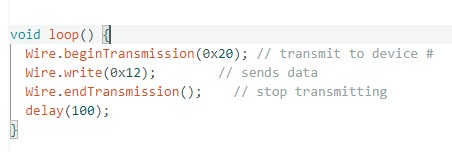

The arduino is programmed using the arduino IDE (see atttached) and is the master.

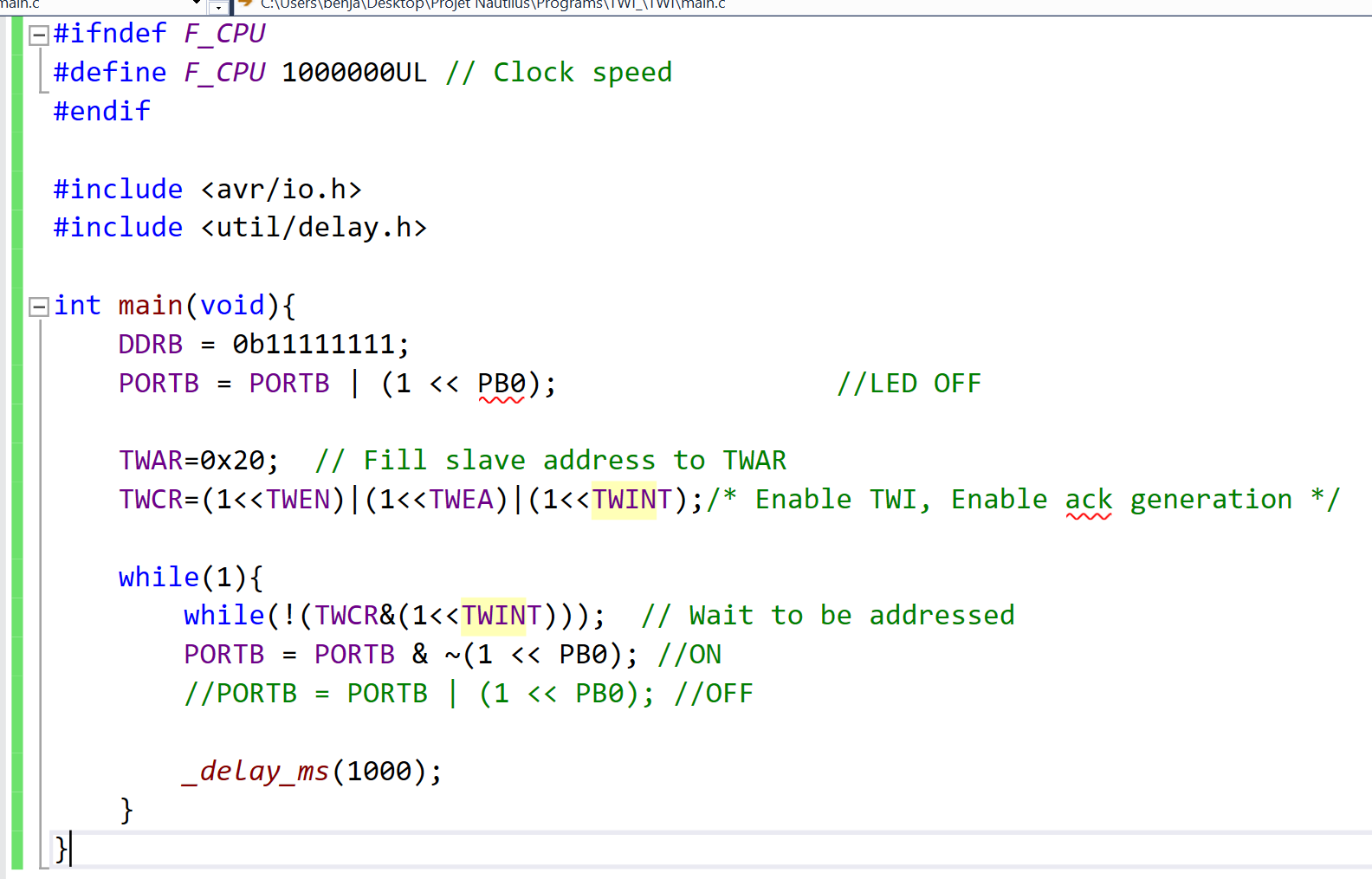

The ATMEGA1284p is programmed using Microchip studio (See attached) and is the slave.

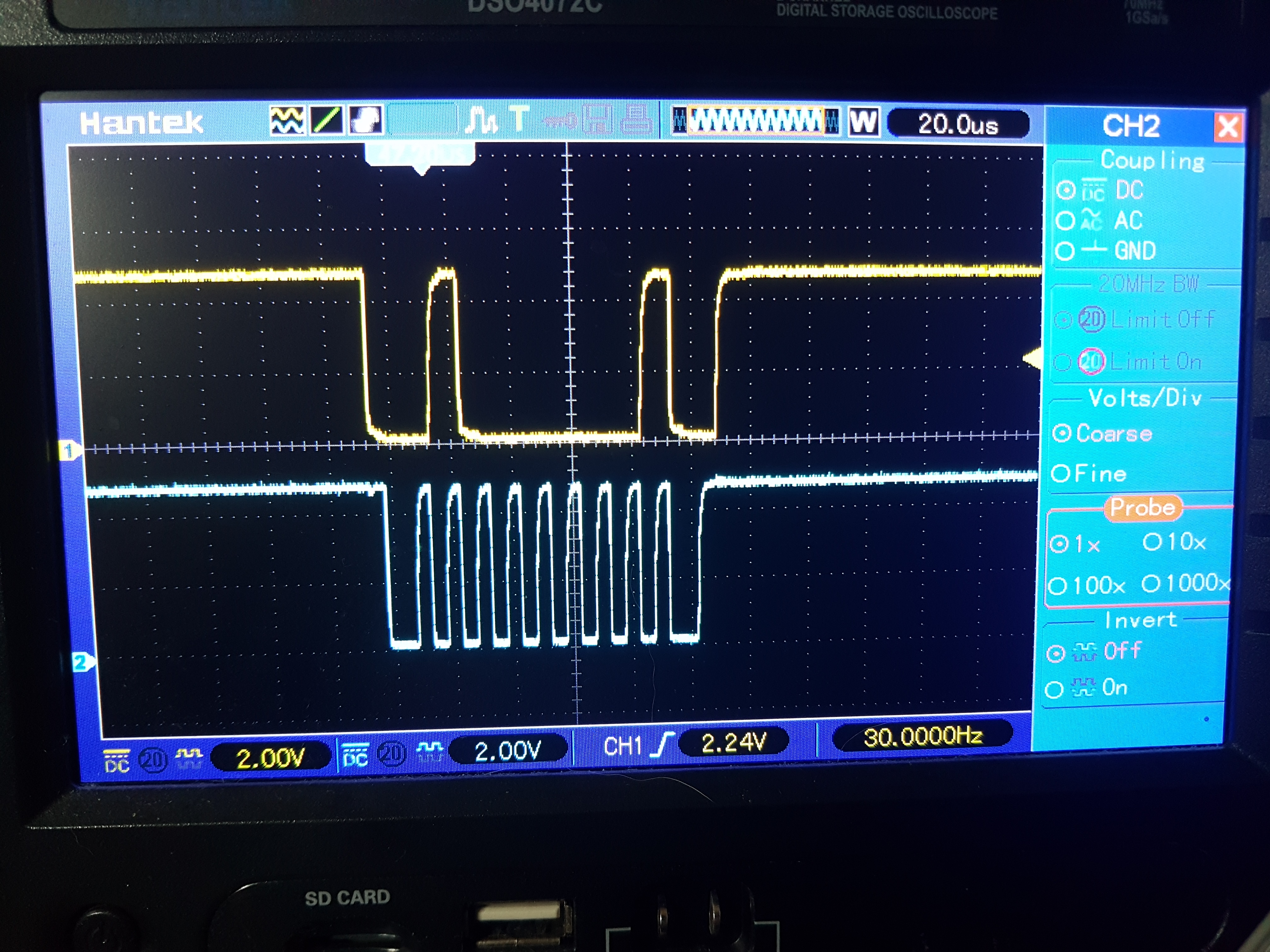

The SDA and SCL line are displayed on the attached SDA_SCL attached file (SCL in blue).

They show the address the master sends to the slave.

The address seems correct (0x20).

But there is no reaction from the slave.

The code of the slave is very simple.

It is just supposed to turn a LED on when it recognized it has been addressed. i.e. after the line

while(!(TWCR&(1<<TWINT)));

However, the slave code never goes beyond this line and the LED never turns ON

On the hardware side, SDA and SCL lines have each a pull-up resistor 2.7kOhm.

Ii would be very gratefull if you could help me finding the issue.

Thank you very much

Best regards

Benjamin

I am trying to create an I2C communication between an arduino mega and an ATMEGA1284p.

The arduino is programmed using the arduino IDE (see atttached) and is the master.

The ATMEGA1284p is programmed using Microchip studio (See attached) and is the slave.

The SDA and SCL line are displayed on the attached SDA_SCL attached file (SCL in blue).

They show the address the master sends to the slave.

The address seems correct (0x20).

But there is no reaction from the slave.

The code of the slave is very simple.

It is just supposed to turn a LED on when it recognized it has been addressed. i.e. after the line

while(!(TWCR&(1<<TWINT)));

However, the slave code never goes beyond this line and the LED never turns ON

On the hardware side, SDA and SCL lines have each a pull-up resistor 2.7kOhm.

Ii would be very gratefull if you could help me finding the issue.

Thank you very much

Best regards

Benjamin