yefj

Advanced Member level 4

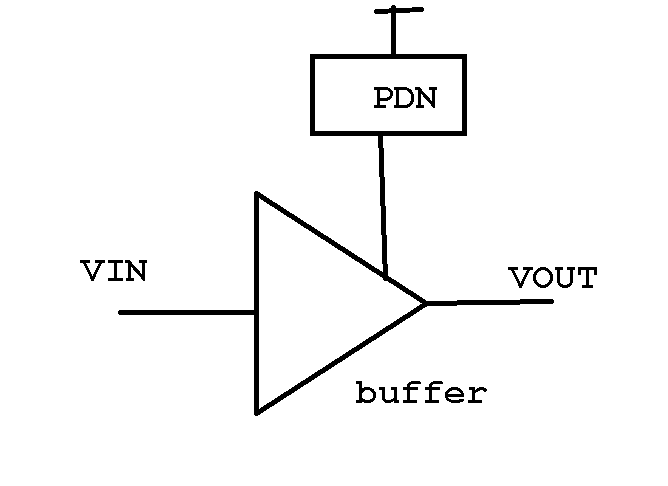

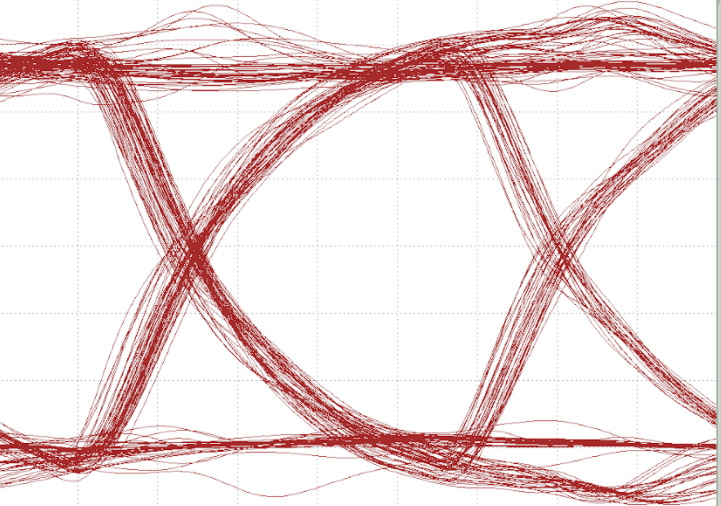

Hello,from the buffer system bellow i get the eye diagram,the problem with this eye diagram is the walls and by their thickness we see the quality of the signal.

What cause the top and bottom wall to get thicker?

I know that if we have higher PDN resistance then Vout capacitor will be charged to less voltage because of voltage divider.

What about the walls on the left and right , the vertical ones

What cause them to get thicker?

Thanks.

What cause the top and bottom wall to get thicker?

I know that if we have higher PDN resistance then Vout capacitor will be charged to less voltage because of voltage divider.

What about the walls on the left and right , the vertical ones

What cause them to get thicker?

Thanks.