melkord

Full Member level 3

Hello,

I am trying to compensate an LDO across all corners.

My boss suggested me that I need to find a correct value for R3 and C3.

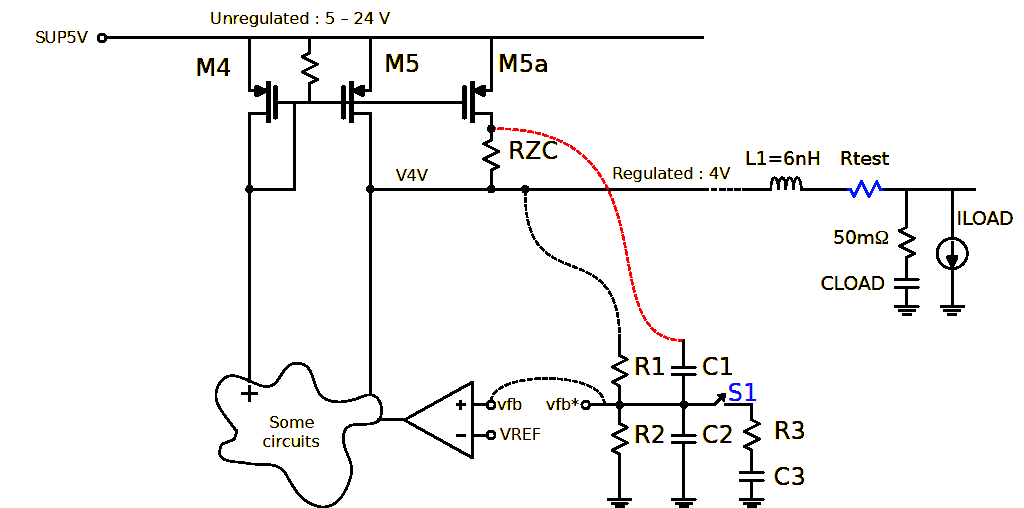

The picture below is the block diagram of the LDO.

My questions:

1. is there a way to find a correct value of R3 and C3 other than trial and error? so far, there are always corners whose PM is still below the spec.

2. I plot the transfer function of vfb*/V4V with different CLOAD when vfb is disconnected from vfb*. I was expecting CLOAD does not effect this transfer function, but it turns out, it does. Any explanation for it?

Thank you.

I am trying to compensate an LDO across all corners.

My boss suggested me that I need to find a correct value for R3 and C3.

The picture below is the block diagram of the LDO.

My questions:

1. is there a way to find a correct value of R3 and C3 other than trial and error? so far, there are always corners whose PM is still below the spec.

2. I plot the transfer function of vfb*/V4V with different CLOAD when vfb is disconnected from vfb*. I was expecting CLOAD does not effect this transfer function, but it turns out, it does. Any explanation for it?

Thank you.