Moskopole

Newbie

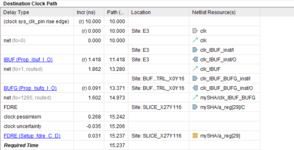

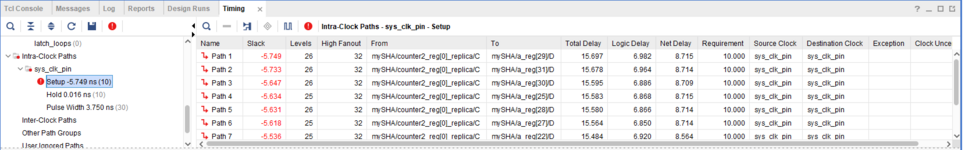

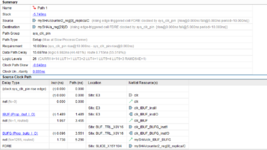

I've been trying to implement a SHA256 design on my Arty a7-35t FPGA. When i try to implement the design, my timing fails wih the following values : WNS: -5.969, TNS : 428. It s my first time encountering this kind of problem and i am not sure how to tackle it. I will post some screenshots under with the error messages that i receive and my Verilog code + testbench .

I've tried adding some pipeline registers but they didnt help, maybe because i dont know where to put them. Thank you in advance.

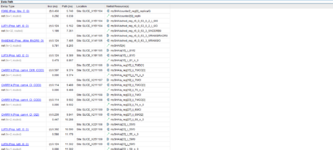

My code contains the following modules:

1.Uart Receiver

2.SHA 256 parser : adds bits until reaches length of 512

3. SHA256_case: does the hashing

4. UART transmitter

I've tried adding some pipeline registers but they didnt help, maybe because i dont know where to put them. Thank you in advance.

My code contains the following modules:

1.Uart Receiver

2.SHA 256 parser : adds bits until reaches length of 512

3. SHA256_case: does the hashing

4. UART transmitter