enemra

Junior Member level 1

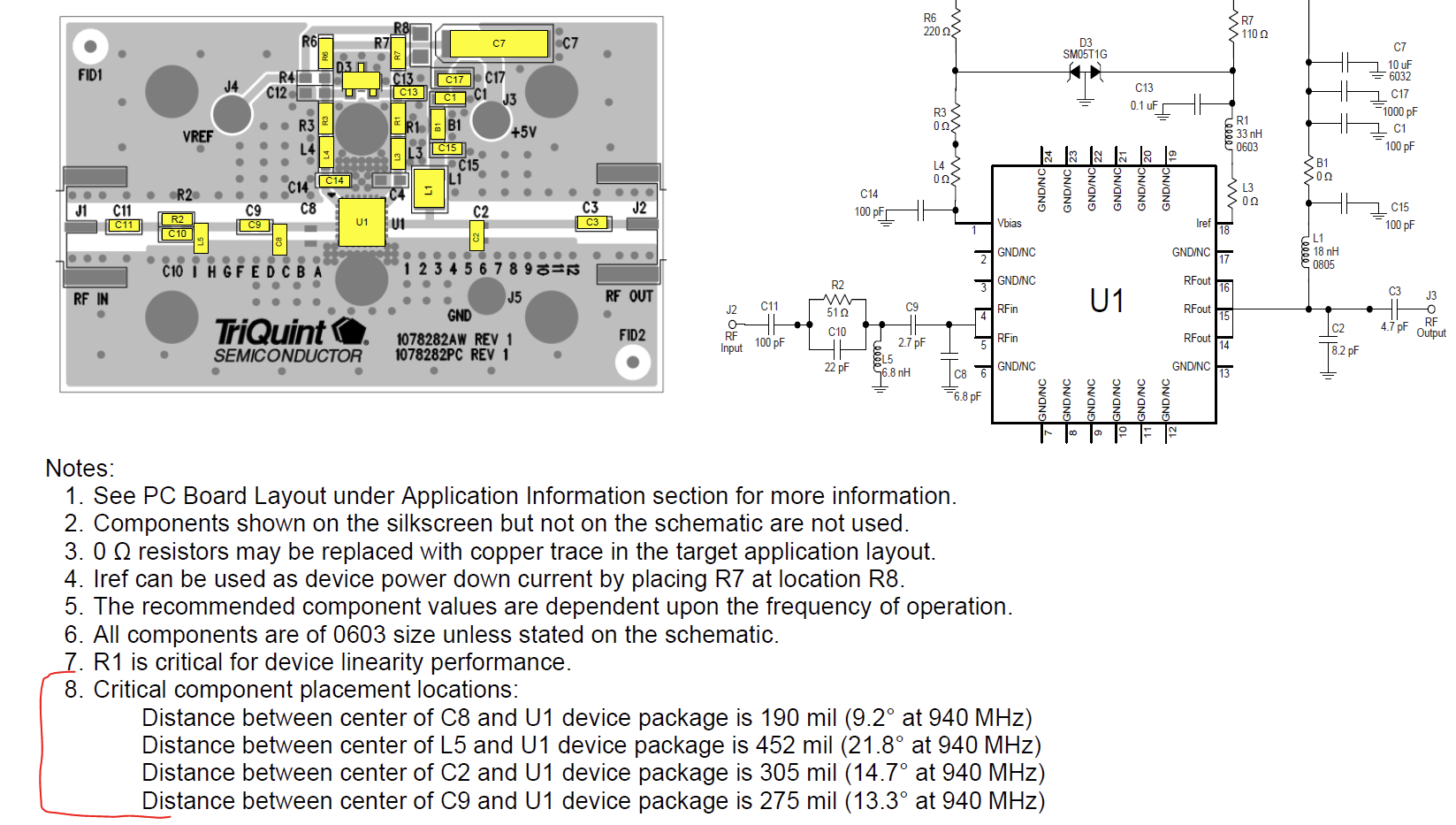

The below screenshot is from TQP7M9104 page-8. Note 8 provides the constraints on the distance between components. If I am not wrong, this is for electrical line distance to control the phase offset. I have two questions wrt this.

1. How can we actually calculate this phase shift for the placement of specific component? Any tool or any pointers to where I can learn?

2. This component is an amplifier and how did the manufacturer come at the number 9.2 deg, 21.8 deg, 14.7 deg, etc?

Thanks in advance

Enemra

1. How can we actually calculate this phase shift for the placement of specific component? Any tool or any pointers to where I can learn?

2. This component is an amplifier and how did the manufacturer come at the number 9.2 deg, 21.8 deg, 14.7 deg, etc?

Thanks in advance

Enemra