ChickenPork

Newbie

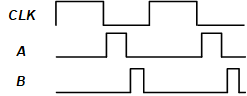

Hi, I'd like to make a control signal that is enabled during the clock falling and turned off before the clock rises.

I tried to make control signals A & B, but i have difficulty making them.

Rules are

1. All signals (including clk) should not overlap

2. A & B are ratioed with respect to CLK. (i.e. A & B's duty is 20% compared to CLK, so whenever CLK frequency changes, A & B should also changes)

3. It's allowed that there exist master clock (i.e. CLK is divided from master clock at least 100 times)

Thank you in advance.

I tried to make control signals A & B, but i have difficulty making them.

Rules are

1. All signals (including clk) should not overlap

2. A & B are ratioed with respect to CLK. (i.e. A & B's duty is 20% compared to CLK, so whenever CLK frequency changes, A & B should also changes)

3. It's allowed that there exist master clock (i.e. CLK is divided from master clock at least 100 times)

Thank you in advance.