quocviet19501

Newbie level 6

Hi all, I'm doing a systemverilog project in designing an asynchronous FIFO.

My design is fine until I have to customize the read pointer for almost_empty reneration.

Here is my code :

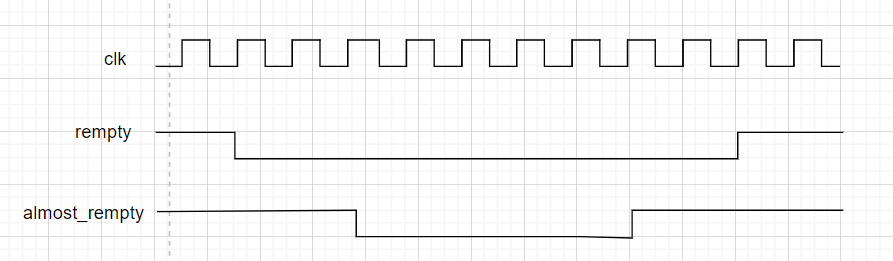

In the testing section I want to make an almost_rempty signal that runs faster than rempty signal 2 clk cycles.

I have tried everything but it did not work.

can anyone siggest an idea how to modify my code.

Thank a lot.

Here is my expected waveform:

My design is fine until I have to customize the read pointer for almost_empty reneration.

Here is my code :

Code Verilog - [expand]

In the testing section I want to make an almost_rempty signal that runs faster than rempty signal 2 clk cycles.

I have tried everything but it did not work.

can anyone siggest an idea how to modify my code.

Thank a lot.

Here is my expected waveform:

Last edited by a moderator: