balabrahmachari

Newbie level 5

hi All,

i have made a 8:1 mux (3 selection lines say three stages )using transmission gates as the switches.

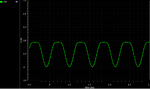

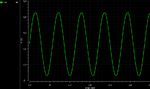

i am getting the THD degraded, at every stage at the switch outputs.

i have observed the input signal is attenuated at the switch outputs.

I am not understand that why the transmission gates wont allow the complete swing of the input?

Can anyone help me please?

thanks in advance...

BALA M..

i have made a 8:1 mux (3 selection lines say three stages )using transmission gates as the switches.

i am getting the THD degraded, at every stage at the switch outputs.

i have observed the input signal is attenuated at the switch outputs.

I am not understand that why the transmission gates wont allow the complete swing of the input?

Can anyone help me please?

thanks in advance...

BALA M..