electronics_rama

Member level 3

Hi All,

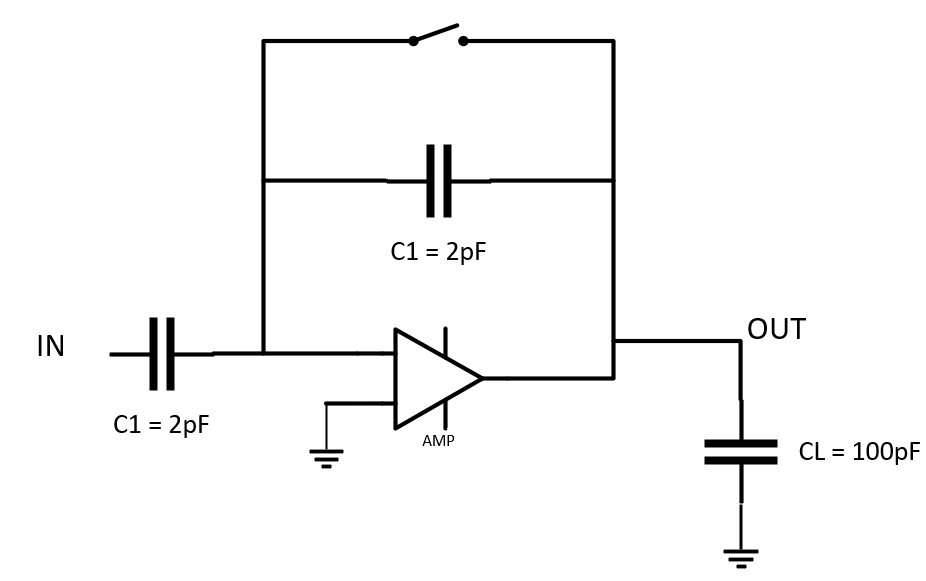

Please find the below structure of a unity gain buffer with a capacitive feedback network. What decides the DC gain and unity gain frequency of the amplifier, "AMP" used in the below circuit?

Thanks.

Please find the below structure of a unity gain buffer with a capacitive feedback network. What decides the DC gain and unity gain frequency of the amplifier, "AMP" used in the below circuit?

Thanks.