ata90

Member level 5

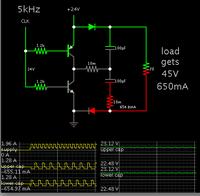

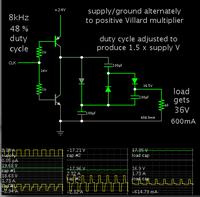

As I considered your simulation, the output is rely on load definitely and whenever the load changes (for example from 80 ohm to 120 ohm), output voltage goes from 38V to 40V. in previous design, we didn't have similar changes to output voltage by variation of load.