promach

Advanced Member level 4

I am recently working on asychronous FIFO coding implementation.

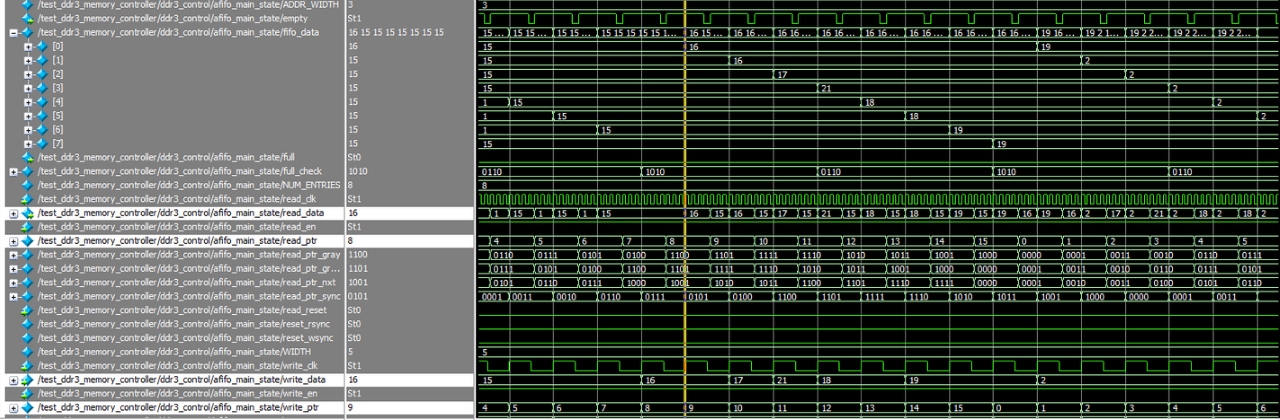

However, I seem to have encountered a common issue with asynchronous FIFO where read_data signal is not really entirely in-phase with read_ptr signal.

For example, read_data could be 15 or 16 for the read_ptr of 9

Someone told me that read_data is only valid when the empty signal is 0 and is undefined/invalid otherwise.

It seems that I need to do some post-processing (using empty signal) on read_data output instead of modifying the logic inside the asynchronous FIFO ?

Is there really a way to keep read_data signal entirely in-phase with read_ptr signal within the asynchronous FIFO ?

Any idea/comments ?

However, I seem to have encountered a common issue with asynchronous FIFO where read_data signal is not really entirely in-phase with read_ptr signal.

For example, read_data could be 15 or 16 for the read_ptr of 9

Someone told me that read_data is only valid when the empty signal is 0 and is undefined/invalid otherwise.

It seems that I need to do some post-processing (using empty signal) on read_data output instead of modifying the logic inside the asynchronous FIFO ?

Is there really a way to keep read_data signal entirely in-phase with read_ptr signal within the asynchronous FIFO ?

Any idea/comments ?

Last edited: