WBrumble

Junior Member level 3

All,

Designing a board for an LED project I'm doing.

The driver is LGA, and combines pins for one signal.

For the pins that are square or rectangular it's okay,

Because I can just spot a SMD pad with the proper

Dimensions and it works well.

But when the pins are not and require a different shape, I

Can't figure it out, ha ha.

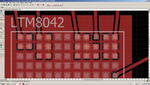

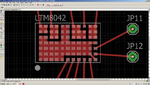

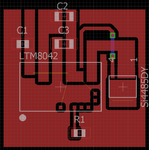

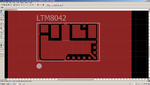

Attached are photos from the data sheet that shows the

Suggested copper layout and in eagle.

What I'm currently doing is putting a rectangular pad on the edge, turning off the stop and cream for the pad, then filling the rest with a polygon of copper. I can then attach a wire to the net in board layout.

But for the ground when I do a ground fill it only attaches to the pin inside the polygon not all of the polygon layout for the ground. And I need to connect all of it for good heat management.

How do you guys do LGA ICs.

Thank you all for your help.

Designing a board for an LED project I'm doing.

The driver is LGA, and combines pins for one signal.

For the pins that are square or rectangular it's okay,

Because I can just spot a SMD pad with the proper

Dimensions and it works well.

But when the pins are not and require a different shape, I

Can't figure it out, ha ha.

Attached are photos from the data sheet that shows the

Suggested copper layout and in eagle.

What I'm currently doing is putting a rectangular pad on the edge, turning off the stop and cream for the pad, then filling the rest with a polygon of copper. I can then attach a wire to the net in board layout.

But for the ground when I do a ground fill it only attaches to the pin inside the polygon not all of the polygon layout for the ground. And I need to connect all of it for good heat management.

How do you guys do LGA ICs.

Thank you all for your help.

Last edited: