Gray Rosewood

Newbie

Greetings, I need guidance to code a question with the requirements listed on the following:

Design a 3-bit dual mode counter that counts

(i) even number in increment order when select=1;

(ii) odd number in decrement order when select=0;

Apart from input select, the counter has a synchronous active-high reset and it is a negative edge triggered synchronous counter.

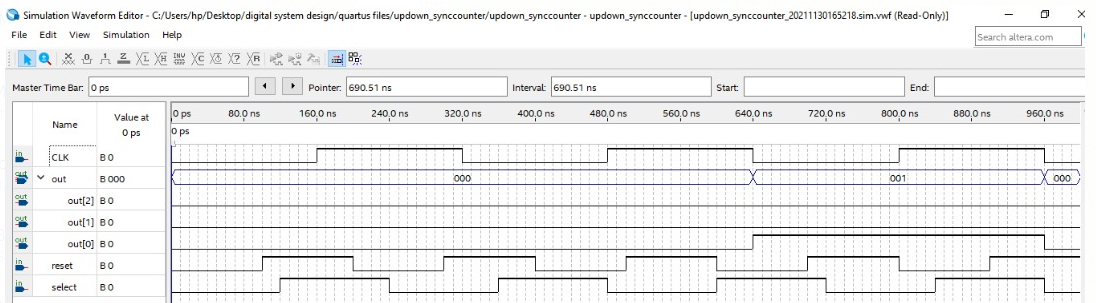

Attached is the code that has been worked on and the corresponding University program waveform output.

Design a 3-bit dual mode counter that counts

(i) even number in increment order when select=1;

(ii) odd number in decrement order when select=0;

Apart from input select, the counter has a synchronous active-high reset and it is a negative edge triggered synchronous counter.

Attached is the code that has been worked on and the corresponding University program waveform output.

Code:

module updown_synccounter (CLK, reset, select, out);// counter has a synchronous

input CLK, reset, select; //active-high reset and it is a negative edge triggered synchronous counter.

output reg [2:0] out;

always@ (negedge CLK)

begin

if (reset==1'b1)

out <=3'b000;

else if (select==1)

out <= out+1;

else

out <= out-1;

end

endmodule

Last edited by a moderator: