TheCPUWizard

Newbie level 5

(a new twist on a common topic)..

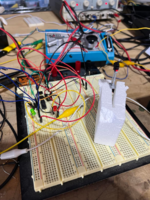

2 wire input. Normally NC between them. Will eventually get a momentary + or - 12V differential between them.... need to set that to a Set/Reset flipflop with TTL (or 3.3V) output...

Many possible circuits, but I am going to need a dozen of these (or more) to monitor sensors - so locking for something that is fairly robust, but also minimizes complexity...

2 wire input. Normally NC between them. Will eventually get a momentary + or - 12V differential between them.... need to set that to a Set/Reset flipflop with TTL (or 3.3V) output...

Many possible circuits, but I am going to need a dozen of these (or more) to monitor sensors - so locking for something that is fairly robust, but also minimizes complexity...