Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

According to datasheet it's a PLL generated carrier. Many small radio PLL transceivers have spurs like this.Transmitter is Si4468

Many small radio PLL transceivers have spurs like this.

Typically, the spur pattern changes when switching the carrier frequency, and it's less regular due to the fractional synthesizer design. So there might be a different reason. Changing the crystal frequency is a useful test to see if the spurious signal is somehow related to PLL operation.I changed frequency twice (860 and 868), but the offset stays the same both times.

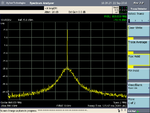

But your signal has still very bad spectral purity.Especially PN seems horrible.I've patched my clock source to go directly to RF clock input and that removed all visible

spurs and reduced noise levels a bit.

So in conclusion there was interference on clock signal due to bad design.

But your signal has still very bad spectral purity.Especially PN seems horrible.

Here is latest measurement with improved levels:

View attachment 132396

Note that span is 2MHz compared to initial!

Datasheet states PN= -105 dBc/Hz at 10kHz offset. So if 1kHz BW then should be -75dBc? And I have -50dBc.

I guess its quite bad if I calculated correclty.