shockingshockley

Member level 1

Hello

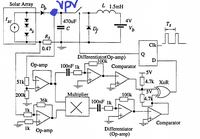

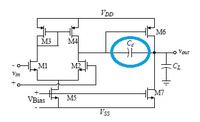

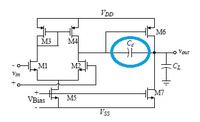

I am implementing my designed two-stage op amp (with a compensating capacitor Cc) as a comparator in my analog circuit.

I run process corners TT, FF, and FS, and my output of the analog circuit is good and okay but not in SF and SS. When I remove the compensating capacitor, the output is now good in SF and SS while not in TT, FF, and FS.

Is there an explanation? Or do I need to redesign. Because the fault in the circuit is in that op amp. Thank you.

I am implementing my designed two-stage op amp (with a compensating capacitor Cc) as a comparator in my analog circuit.

I run process corners TT, FF, and FS, and my output of the analog circuit is good and okay but not in SF and SS. When I remove the compensating capacitor, the output is now good in SF and SS while not in TT, FF, and FS.

Is there an explanation? Or do I need to redesign. Because the fault in the circuit is in that op amp. Thank you.