patan.gova

Full Member level 3

Hello,

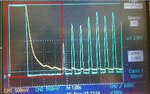

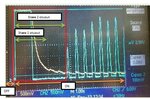

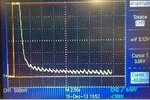

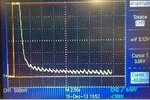

I am working with the pulse signals.My circuit is working fine but the output of the photodiode (pulse signal) is taking some settling time(shown with RedBox in the attached image) to come a an standard voltage level.

in the attached image) to come a an standard voltage level.

The output of the photodiode will be taken by switching it ON and OFF for some particular interval.I want to remove this settling time because when I want to take the output signal after 10sec of switching it ON then I don't get desired pulse signal as this will be still in settling stage.

Can anyone suggest how to remove the settling time.

Thanks.

I am working with the pulse signals.My circuit is working fine but the output of the photodiode (pulse signal) is taking some settling time(shown with RedBox

in the attached image) to come a an standard voltage level.

in the attached image) to come a an standard voltage level.The output of the photodiode will be taken by switching it ON and OFF for some particular interval.I want to remove this settling time because when I want to take the output signal after 10sec of switching it ON then I don't get desired pulse signal as this will be still in settling stage.

Can anyone suggest how to remove the settling time.

Thanks.