Shady Ahmed

Member level 5

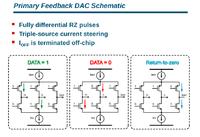

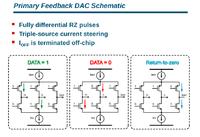

Based on what i understand from the following architecture , i started the Current steering DAC design

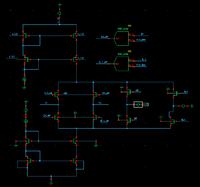

I calculated the current as ((1.2-0.6)/R) / 2 ) ... (the 2 multiplied is for the compensation (because it is RZ).

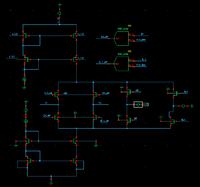

As u can see, i designed the Cascode mirrors with 1.1 Mohm & 800 KOhm for the NMOS & PMOS respectively.

The 2 branches to the right are to dissipate the current and don't push it to the summing node in the 2 cases ( D0 is high and Clock is High )

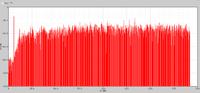

Here is the DAC DC analysis (image 1 )

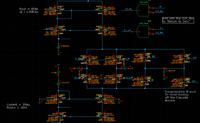

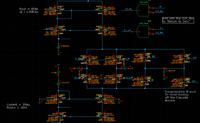

And here is the DAC inserted to the system ( image 2)

where V+ & V- are the summing nodes

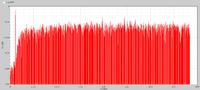

However , when i used it in the system , the SQNR is decreased by 17 db or so ...

Here are FFT for the O/P using the IDEAL DAC (the first figure , SNR = 78.6 dB ) & CURRENT STEERING DAC (the second figure , SNR = 60.7 dB) - with the same differential input (0.45)

If it helps.

- - - Updated - - -

I used this architecture

I calculated the current as ((1.2-0.6)/R) / 2 ) ... (the 2 multiplied is for the compensation (because it is RZ).

As u can see, i designed the Cascode mirrors with 1.1 Mohm & 800 KOhm for the NMOS & PMOS respectively.

The 2 branches to the right are to dissipate the current and don't push it to the summing node in the 2 cases ( D0 is high and Clock is High )

Here is the DAC DC analysis (image 1 )

And here is the DAC inserted to the system ( image 2)

where V+ & V- are the summing nodes

However , when i used it in the system , the SQNR is decreased by 17 db or so ...

Here are FFT for the O/P using the IDEAL DAC (the first figure , SNR = 78.6 dB ) & CURRENT STEERING DAC (the second figure , SNR = 60.7 dB) - with the same differential input (0.45)

If it helps.

- - - Updated - - -

I used this architecture