syedshan

Advanced Member level 1

- Joined

- Feb 27, 2012

- Messages

- 463

- Helped

- 27

- Reputation

- 54

- Reaction score

- 26

- Trophy points

- 1,308

- Location

- Jeonju, South Korea

- Activity points

- 5,134

Dear all,

I am having problem with getting data from my ADC... please see the following

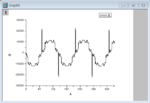

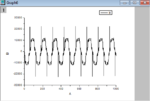

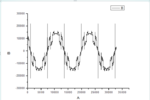

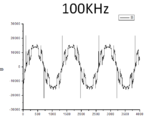

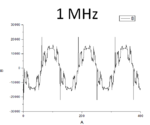

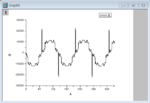

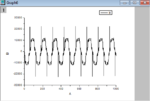

I am giving 125Mhz Sampling clock to1 Mhz Sine wave signal. The image attached is the response that I am getting.

What are these Sudden Jerks or Instant rise or Falls... Is it because of sampling frequency bei

In actual I have to give different signal, but I am having this same Jerks problem with that as well, so I tried it with simple sine wave.

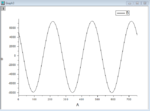

Also When my sampling frequency is 250 Mhz the things are fine...

Please eagerly waiting for response

I am having problem with getting data from my ADC... please see the following

I am giving 125Mhz Sampling clock to1 Mhz Sine wave signal. The image attached is the response that I am getting.

What are these Sudden Jerks or Instant rise or Falls... Is it because of sampling frequency bei

In actual I have to give different signal, but I am having this same Jerks problem with that as well, so I tried it with simple sine wave.

Also When my sampling frequency is 250 Mhz the things are fine...

Please eagerly waiting for response