iVenky

Advanced Member level 2

- Joined

- Jul 11, 2011

- Messages

- 584

- Helped

- 37

- Reputation

- 76

- Reaction score

- 35

- Trophy points

- 1,318

- Location

- College Station, Texas

- Activity points

- 6,124

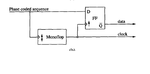

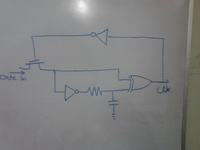

I am doing the IC design for data and clock recovery of Ask waveform of a Manchester coded data. I have no problem with the demodulation of Ask waveform to Manchester coded format. Now I want to recover the clock from the Manchester coded format and I am finding it really difficult. I have searched many IEEE papers. All those specify that I need a mono-flop (i.e. it will respond only for a certain period of time and if any trigger is there, a high/low voltage pulse will be the output.(during which it will not respond). ) I need the exact circuit to implement this operation. Note that there is no PLL involved.

How do you recover clock usually from a Manchester coded data as in passive RFID tags?

Thanks in advance.

How do you recover clock usually from a Manchester coded data as in passive RFID tags?

Thanks in advance.