edaenrico

Member level 4

Hi,

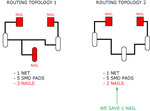

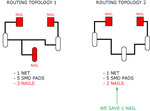

I've been wondering if the routing my boards in a certain way makes me save money on the PCB Bare board tests.

I route the board in order to have the minimal number of end points as possible.

Each end point will require a nail in the fixture.

The questions are:

1) Having fewer nails is good or not for the tests?

2) Do bare PCB tests cost less if the PCB require less nails?

Thanks,

Enrico Migliore

I've been wondering if the routing my boards in a certain way makes me save money on the PCB Bare board tests.

I route the board in order to have the minimal number of end points as possible.

Each end point will require a nail in the fixture.

The questions are:

1) Having fewer nails is good or not for the tests?

2) Do bare PCB tests cost less if the PCB require less nails?

Thanks,

Enrico Migliore