afz23

Full Member level 3

very high loop bandwidth + pll

I am designing a programmable PLL based frequency synthesizer.

I am using intger-N PLL,right now only this PLL is available for project.

Fout=4000 to 4500 MHz

N= 32000 to 36000

Fcomp=125 KHz ( reference)

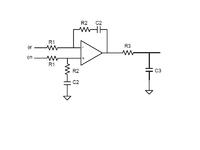

I designed loopfilter for BW=10KHz ,order 3 active type,but the

reference spurs are very high not at all acceptable.

I tried with order 4 also,it also didn't heped much.

Division ratio being very high (20logN>90dB) is also not

helping.

All you PLL experts please help me in solving this, and get rid of these

refrence spurs.

If any body has some literature which specifically deals with very high

division ratio,please give me that.

I am designing a programmable PLL based frequency synthesizer.

I am using intger-N PLL,right now only this PLL is available for project.

Fout=4000 to 4500 MHz

N= 32000 to 36000

Fcomp=125 KHz ( reference)

I designed loopfilter for BW=10KHz ,order 3 active type,but the

reference spurs are very high not at all acceptable.

I tried with order 4 also,it also didn't heped much.

Division ratio being very high (20logN>90dB) is also not

helping.

All you PLL experts please help me in solving this, and get rid of these

refrence spurs.

If any body has some literature which specifically deals with very high

division ratio,please give me that.