Electric_Shock

Junior Member level 2

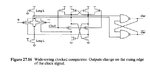

I follow the output offset cancellation OOS scheme for the pre-amplier of a dynamic comparator. I use non-overlapping clock to control switches: (clk1 & clk1_n) control S1 S2 S3 S4 non-overlap with (clk2 & clk2_n) for 2 switches at Vin. But I notice that during the non-overlap time between 2 clock, the input of differential pair look like to be floating so the voltage at these nodes change undesirably like in the waveform. How do I solve this issues ?