kthackst

Member level 5

I'm having issues reliably making J-inverters around 350 MHz.

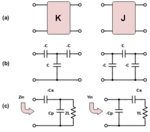

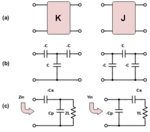

In previous applications in my work, we've needed inverters in low frequencies (1-10MHz) that are easily realizable using lumped elements. We use a half pi network which I show below for both K inverters and J inverters.

For the low frequencies this is easy because we can use 0201 surface mount capacitors to make our inverters; typically these are in the range of 100-10,000 pF.

For very high frequencies in the GHz, I understand it makes much more sense to use a quarter wave transformer for an inverter.

But I'm trying now to design an inverter around 350 MHz and the capacitor values to realize it are on the order of 0.2-6 pF! The error I introduce simply soldering these components on the board is on this order of magnitude; I find myself removing and adding on different capacitors of the same value until I get lucky with the tolerance. Clearly achieving my actual characteristic impedance/admittance is very difficult when it depends so much on hundreds of femto Farads. But this frequency still is too small for me to make a quarter wave transformer that can fit on our small device (~15 mm long).

Can anyone suggest a different way to realize inverters that I can design to a higher tolerance without leaving an enormous footprint on my device?

In previous applications in my work, we've needed inverters in low frequencies (1-10MHz) that are easily realizable using lumped elements. We use a half pi network which I show below for both K inverters and J inverters.

For the low frequencies this is easy because we can use 0201 surface mount capacitors to make our inverters; typically these are in the range of 100-10,000 pF.

For very high frequencies in the GHz, I understand it makes much more sense to use a quarter wave transformer for an inverter.

But I'm trying now to design an inverter around 350 MHz and the capacitor values to realize it are on the order of 0.2-6 pF! The error I introduce simply soldering these components on the board is on this order of magnitude; I find myself removing and adding on different capacitors of the same value until I get lucky with the tolerance. Clearly achieving my actual characteristic impedance/admittance is very difficult when it depends so much on hundreds of femto Farads. But this frequency still is too small for me to make a quarter wave transformer that can fit on our small device (~15 mm long).

Can anyone suggest a different way to realize inverters that I can design to a higher tolerance without leaving an enormous footprint on my device?