kokei74

Junior Member level 3

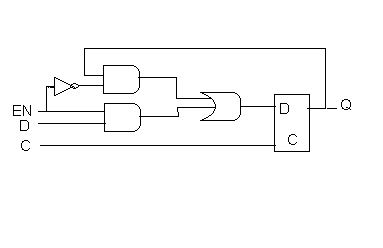

hi, im quite new to VHDL and currently is learning now. I try to create a D flip flop with enable from a D flip flop using a port map.

here is VHDL for DFF

library ieee;

use ieee.std_logic_1164.all;

entity dfflop is

port (D,clock :IN std_logic;

Q :OUT std_logic);

end dfflop;

architecture logic of dfflop is

begin

process (clock)

begin

if clock'event AND clock = '1' THEN

Q <= D;

end if;

end process;

end logic;

Here is VHDL for DFF with enable.

library ieee;

use ieee.std_logic_1164.all;

entity DFF_en is

port (EN,D0,C :IN std_logic;

Q0 :OUT std_logic);

end DFF_en;

architecture logic of DFF_en is

signal p0 : std_logic;

component dfflop

port (D,clock :IN std_logic;

Q :OUT std_logic);

end component;

begin

p0 <= (NOT EN AND Q0)OR(EN AND D0);

stage0 : dfflop port map (p0,C,Q0);

end logic;

when start compilation this error occur.

Error: VHDL Interface Declaration error in DFF_en.vhd(21): interface object "Q0" of mode out cannot be read. Change object mode to buffer or inout.

Error: Ignored construct logic at DFF_en.vhd(11) because of previous errors

Please help me verify what is the problem. Thx

here is VHDL for DFF

library ieee;

use ieee.std_logic_1164.all;

entity dfflop is

port (D,clock :IN std_logic;

Q :OUT std_logic);

end dfflop;

architecture logic of dfflop is

begin

process (clock)

begin

if clock'event AND clock = '1' THEN

Q <= D;

end if;

end process;

end logic;

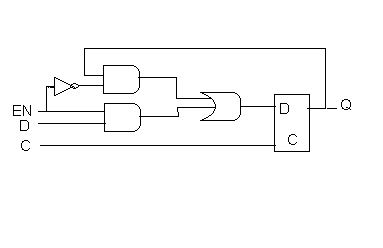

Here is VHDL for DFF with enable.

library ieee;

use ieee.std_logic_1164.all;

entity DFF_en is

port (EN,D0,C :IN std_logic;

Q0 :OUT std_logic);

end DFF_en;

architecture logic of DFF_en is

signal p0 : std_logic;

component dfflop

port (D,clock :IN std_logic;

Q :OUT std_logic);

end component;

begin

p0 <= (NOT EN AND Q0)OR(EN AND D0);

stage0 : dfflop port map (p0,C,Q0);

end logic;

when start compilation this error occur.

Error: VHDL Interface Declaration error in DFF_en.vhd(21): interface object "Q0" of mode out cannot be read. Change object mode to buffer or inout.

Error: Ignored construct logic at DFF_en.vhd(11) because of previous errors

Please help me verify what is the problem. Thx