jgk2004

Full Member level 5

- Joined

- Dec 1, 2009

- Messages

- 274

- Helped

- 77

- Reputation

- 154

- Reaction score

- 74

- Trophy points

- 1,308

- Location

- Munich Germany

- Activity points

- 3,520

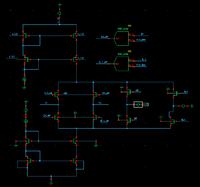

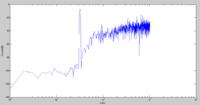

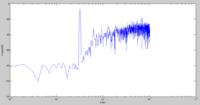

first, the problem I see is, you put a step pulse to your integrator, therefore, it should integrate with a slow due to the current and the C. Since you have feedback around your amplifier, this should result in the summation node staying at VDD/2 with only a small ripple. If its moving like what you have, you need to find out why... If you put in an ideal amplifier again, does it do the same thing?? Do this to check.

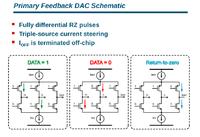

second, is your DAC a current steering DAC or a switched resistor DAC? If its a current steering DAC NO resistors are there, just two cells. If its a switched resistor DAC you should have 2 resistors in each cell for a 1.5Bit switching.. then you would need reference voltages.

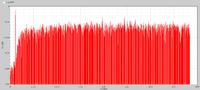

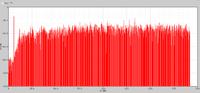

Last, as for testing your DAC you need to test it in your entire ADC with all other blocks being verilogA modeled.. I know it takes time but that is the hard part about designing DSMs. If you have a DAC in place, switching a ~380MHz, I would say like 4 hours for a good spectrum. If you include the amplifier maybe another 2 hours. Trust me this is still short. When you finish the entire ADC and simulate with parasitics it can take easily 4 days to a week!!!!!

JGK

second, is your DAC a current steering DAC or a switched resistor DAC? If its a current steering DAC NO resistors are there, just two cells. If its a switched resistor DAC you should have 2 resistors in each cell for a 1.5Bit switching.. then you would need reference voltages.

Last, as for testing your DAC you need to test it in your entire ADC with all other blocks being verilogA modeled.. I know it takes time but that is the hard part about designing DSMs. If you have a DAC in place, switching a ~380MHz, I would say like 4 hours for a good spectrum. If you include the amplifier maybe another 2 hours. Trust me this is still short. When you finish the entire ADC and simulate with parasitics it can take easily 4 days to a week!!!!!

JGK