Junus2012

Advanced Member level 5

Hello Analog heroes

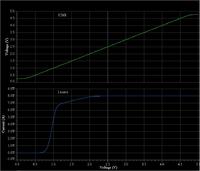

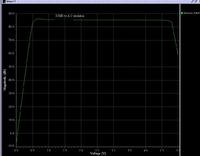

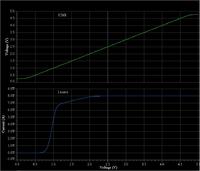

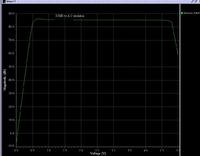

I finished design of an NMOS input OTA, I used a cascode current source and I was expecting to get bad low ICMR, but I surprised with the result. as you can see the cascod current source start to saturate at 2.3V while the ICMR start showing linear behavioural at 0.25V. then I did the ICMR test by sweeping the VCM from the A.C analyses as shown in the second image, the result always the same

What are the reason behind that?

Thank you very much

I finished design of an NMOS input OTA, I used a cascode current source and I was expecting to get bad low ICMR, but I surprised with the result. as you can see the cascod current source start to saturate at 2.3V while the ICMR start showing linear behavioural at 0.25V. then I did the ICMR test by sweeping the VCM from the A.C analyses as shown in the second image, the result always the same

What are the reason behind that?

Thank you very much