Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

Do I see correctly that the trace is folding over on itself? That's impressive... but you probably don't think so. I've never seen anything like this before. Can you supply schematic? What type of amplifier is this? Is this a linear, non-linear or ... simulation?

Simulation setup has some erros.90 degree Coupler and Combiner circuits have been defined for RF frequencies, at DC they may be trouble by definition..Yes you see correctly.

This is a non linear HEMT GaN 50 W amplifier operating from 10MHz to 700 MHz.

View attachment 81699

The PAE plot is correct, maybe the fall at the end is a little bit accentuated.

Because PAE=(Pout-Pinp)/Pdc when the PA goes near saturation and over, when you increase the Pinp the Pout remain the same and the PAE goes down.

Just search the net for Power Added Efficiency images and you get similar plots.

**broken link removed**

Simulation setup has some erros.90 degree Coupler and Combiner circuits have been defined for RF frequencies, at DC they may be trouble by definition..

That's why supply circuits should be added externally for a proper bias.

I'm saying that you supply MOS through Balun circuits but these circuits are effectively defined for RF/AC signals that's why , your simulator will do an interpolation at DC and the results may be erroneous.BigBoss, i did not post the supply circuit, here it is. I don't have any 90 degree coupler at the output, it is a balun (180 degree. )

I'm saying that you supply MOS through Balun circuits but these circuits are effectively defined for RF/AC signals that's why , your simulator will do an interpolation at DC and the results may be erroneous.

Consider the circuits equations are limited by frequency of these kind of circuits.

Thanks BigBoss, in the DC decoupling circuit I have a 1uH inductor for the drain, and in my output circuit i have bypass capacitors. Is it similar to the picture you post? I believe DC_feed component from ADS is actually a 1uH inductor.

DC block is an ideal component so that inductance value-for instance- 1H

Coupling component is also an ideal element that has-for instance- 1F

There isn't any constraint to use these component.Af

If we logically consider your PAE curve, can the effciency be 0% ?? at 15dBm Output Power ??I tried to replace the bypass capacitors I have and the inductors by these components and the PAE trend is the exactly the same. My conclusion is that the DC power is probably properly computed.

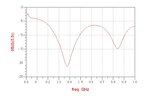

If we logically consider your PAE curve, can the effciency be 0% ?? at 15dBm Output Power ??

There are still erroneous points..

I plotted Pout and PAE vs Pin :

View attachment 81975