carwe

Newbie level 2

- Joined

- Jan 3, 2011

- Messages

- 2

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

- 1,396

Hi,

I'm having some problems to understand the exact behavior of the ISERDESE2 primitive. What I need to understand is exactly how the unit will distribute the serial input to the bits in the output (paralell) words, or in other words, how ISERDESE aligns the frames on the incoming serial data stream in order to deliver the paralell words.

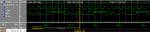

Here is a screenshot showing the signals on some of the ports of a cascaded (width expansion) ISERDES-pair:

This example is actually from a simulation of the example design that is generated by Coregen (SelectIO Interface Wizard). Width is 14 bits, DDR mode. The VHDL code is inserted below this message.

The signal iserdes_q_vec is a vector [slave q8..q3] & [master q8..q1].

From the input (ddly) and output (iserdes_q_vec) I can clearly see how the frame is aligned - I have marked the frame by the two cursors. It is clear that the ddly input within this frame (10000111100100) is what appears on iserdes_q_vec on the next rising edge of clkdiv.

The reason for this particular alignment is however unknown to me. I've looked in the User Guide (ug471) but can't find info on this.

I tried to de-assert rst in various ways but couldn't really make anything out of the results (in this design, rst is de-asserted synchronously with clkdiv, as suggested by the user guide).

In my case, I have no training pattern and hance can't find the right alignment with bitslip operations. In my case, for the serial data, clkdiv is equal to the frame clock. From the simulation I can of course determine how the frame is placed in the serial data, and fix the paralell words in custom logic, but then I need to understand why I get this particular offset, and be convinced that I will always get exactly this particular offset.

I would intuitively have expected clkdiv to act as a frame clock as well, but nothing in the UG suggests that, and according to the simulation, that is also clearly not the case.

Device: xc7k160t-2

Thanks in advance,

Carl

I'm having some problems to understand the exact behavior of the ISERDESE2 primitive. What I need to understand is exactly how the unit will distribute the serial input to the bits in the output (paralell) words, or in other words, how ISERDESE aligns the frames on the incoming serial data stream in order to deliver the paralell words.

Here is a screenshot showing the signals on some of the ports of a cascaded (width expansion) ISERDES-pair:

This example is actually from a simulation of the example design that is generated by Coregen (SelectIO Interface Wizard). Width is 14 bits, DDR mode. The VHDL code is inserted below this message.

The signal iserdes_q_vec is a vector [slave q8..q3] & [master q8..q1].

From the input (ddly) and output (iserdes_q_vec) I can clearly see how the frame is aligned - I have marked the frame by the two cursors. It is clear that the ddly input within this frame (10000111100100) is what appears on iserdes_q_vec on the next rising edge of clkdiv.

The reason for this particular alignment is however unknown to me. I've looked in the User Guide (ug471) but can't find info on this.

I tried to de-assert rst in various ways but couldn't really make anything out of the results (in this design, rst is de-asserted synchronously with clkdiv, as suggested by the user guide).

In my case, I have no training pattern and hance can't find the right alignment with bitslip operations. In my case, for the serial data, clkdiv is equal to the frame clock. From the simulation I can of course determine how the frame is placed in the serial data, and fix the paralell words in custom logic, but then I need to understand why I get this particular offset, and be convinced that I will always get exactly this particular offset.

I would intuitively have expected clkdiv to act as a frame clock as well, but nothing in the UG suggests that, and according to the simulation, that is also clearly not the case.

Device: xc7k160t-2

Thanks in advance,

Carl

Code VHDL - [expand]

Last edited by a moderator: