Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

... the vgs of the input devices is less than vth, i think the voltage at the source must be equal to vg-vth.

... how could this happen? it's not reasonable

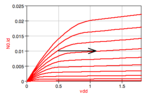

Sure it is: your input diff pair (with Veff=vgs-vth = -80mV) is operating in weak inversion mode, which is quite normal for MOSFETs with low Ids and high W/L ratios (input stages).

Yes. gm/Id gets its maximum in weak inversion = subthreshold region, however.... does that mean if i want to increase gm, i have to increase current.

Yes. gm/Id gets its maximum in weak inversion = subthreshold region, however.

Try and grant it some more current.Maybe that's part of the reason why the sampling clock of my switched-cap opamp can't run at 10MHz even the small signal unity frequency looks good(>100MHz).

To get enough gm from the input stage, you have to shift it into saturation region by decreasing its Vgs.i thought this diff-pair was in saturation region, while it is not.

Try and grant it some more current.

To get enough gm from the input stage, you have to shift it into saturation region by decreasing its Vgs.

if i increase current I ... my Vgs-Vth is increaes too since W/L is fixed. why?

yes, but you said by decreasing vgs to get gm in saturation in the reply above, so i am confused

... so I think you wanted to get out of the linear into the saturation region, which I also recommended to increase gm.i thought this diff-pair was in saturation region, while it is not.

my W/L=160µ/0.5µ in a 130nm process.

How it can be 130nm process with L=0.5µ?