Alex_Zhan

Newbie level 6

Dear everyone,

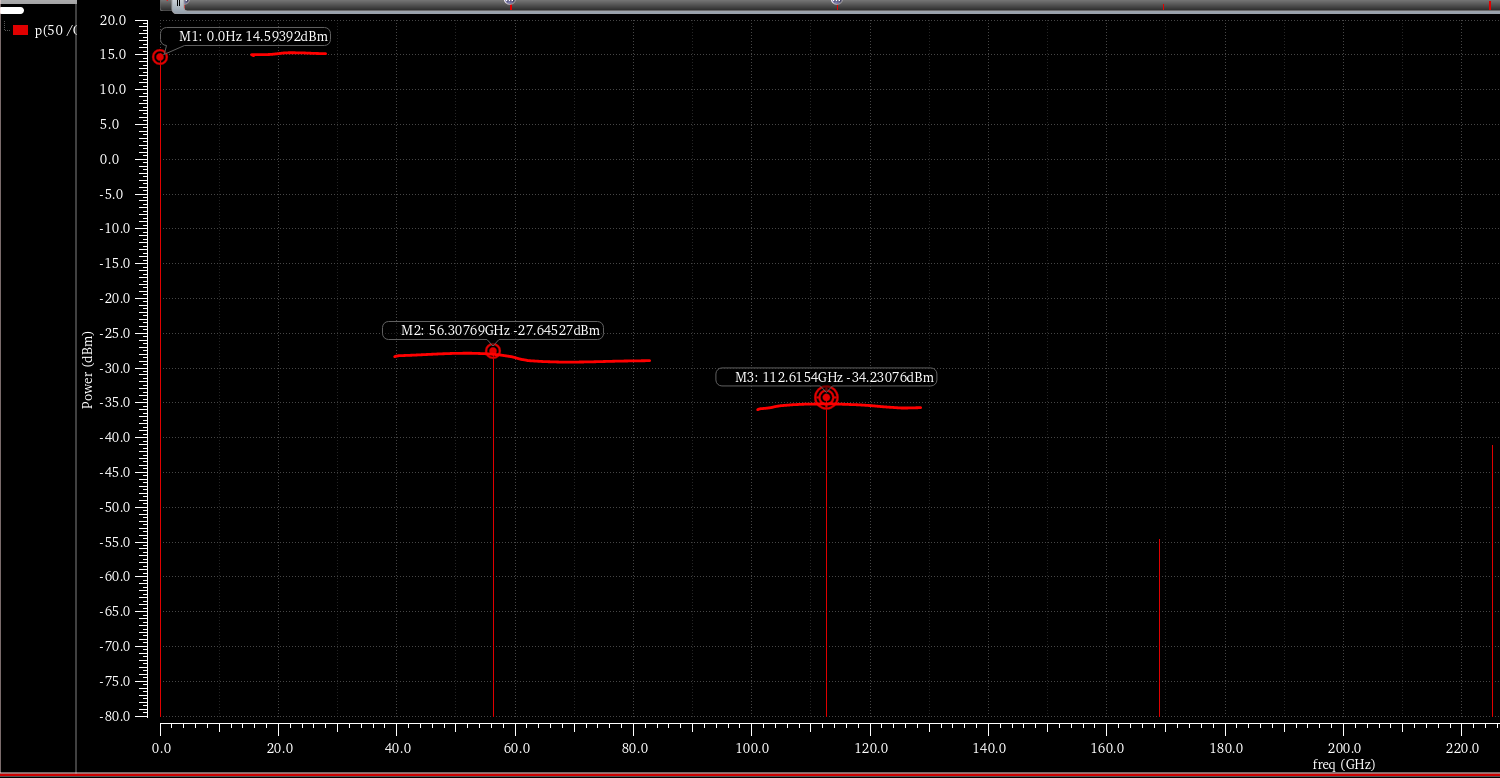

I have designed a VCO operating at ~60GHz, the DC power at the output net is 14.6dBm, while the power of fundamental wave is only ~27.6 dBm? Does anyone know the reason?

Here is the output power, thanks very much!

I have designed a VCO operating at ~60GHz, the DC power at the output net is 14.6dBm, while the power of fundamental wave is only ~27.6 dBm? Does anyone know the reason?

Here is the output power, thanks very much!

--- Updated ---

-27.6 dBm~27.6 dBm