liletian

Full Member level 6

Hi Guys

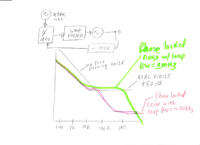

I had a questions, the PLL will help to filter out the output phase noise at frequency winthin PLL the low pass filter. Then why not design a PLL with high loop bandwith of low pass filter? As I know, the low pass filter bandwidth is normally 10 to 100 KHz. Why choosing such a low bandwidth? Why not use a bandwidth of 10MHz or even more to help the output phase noise?

Thanks

I had a questions, the PLL will help to filter out the output phase noise at frequency winthin PLL the low pass filter. Then why not design a PLL with high loop bandwith of low pass filter? As I know, the low pass filter bandwidth is normally 10 to 100 KHz. Why choosing such a low bandwidth? Why not use a bandwidth of 10MHz or even more to help the output phase noise?

Thanks