rmanalo

Advanced Member level 4

- Joined

- Feb 8, 2017

- Messages

- 107

- Helped

- 16

- Reputation

- 32

- Reaction score

- 16

- Trophy points

- 18

- Location

- Philippines

- Activity points

- 979

Hello everyone,

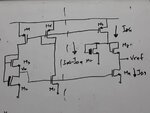

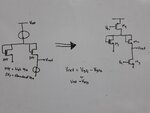

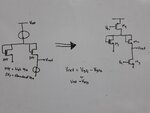

I'm working on subthreshold circuits as part of my project. The image bellow shows Vref as a temperature compensated reference and M3 and M4 as current sources mirrored from a current generator.

I have simulated the circuit and achieved a temperature compensated Vref. By following the equation,

Vref=Vgs1-Vgs2

Vref=Vth1-Vth2+m*Vt*ln[(W/L)2/(W/L)1]

But Vref is also equal to Vds3. How can I explain that Vref is controlled by M1 and M2 and not a function of the drain-source voltage of M3?

Please correct me if my understanding is wrong. Thanks.

Best regards,

rmanalo27

I'm working on subthreshold circuits as part of my project. The image bellow shows Vref as a temperature compensated reference and M3 and M4 as current sources mirrored from a current generator.

I have simulated the circuit and achieved a temperature compensated Vref. By following the equation,

Vref=Vgs1-Vgs2

Vref=Vth1-Vth2+m*Vt*ln[(W/L)2/(W/L)1]

But Vref is also equal to Vds3. How can I explain that Vref is controlled by M1 and M2 and not a function of the drain-source voltage of M3?

Please correct me if my understanding is wrong. Thanks.

Best regards,

rmanalo27