Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

Hello raika,

If I am not wrong then you can not comment on the delay of a circuit just by looking at the technology because delay of circuit depends on a lot of parameters namely current burned, MOSFET size, I/P signal slew and O/P load capacitor. You can have same delay in a 130nm ckt as in 90nm ckt if the above factors are properly manipulated.

But in general delay should be less in 90nm .... but a fixed value for it should be hard to comment ... If you can specify your target delay then we can suggest whether 90nm will work or not ...

Hope this will help ...

So why don't you analyze it by a simulator tool?

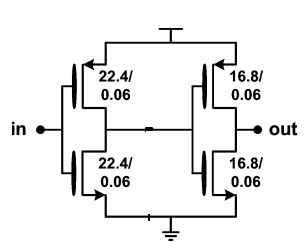

And why would you make the input inverter stronger than the output inverter? And why symmetrical (PMOS/NMOS) ?

Hi raika,

As we don't know about the reference that you have followed it would be difficult to judge in what context they have mentioned 40ps.

If the simulation results are 24ps then it is 24ps. BUT do check your load capacitor. About sizing I would like to say that the general practice is to keep PMOS size = 2 or 3 times NMOS size (depending on the mobility ratio in that technology). This gives the trip point of the buffer at VDD/2 (approx). But you are free to choose any size if trip point voltage requirement is higher or lower.