draser

Member level 2

Hello,

In my design i get some vital glitches and i think i know where do they come from.

Lets assume that i have a combinational circuit with INPUTS A,B,C and an OUTPUT E that depends from every input.These inputs are connected with flip flops but each flip flop is a part of a different component.

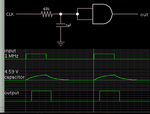

My problem is that the input A is changing i.e. at 0.01 ns ,the input B at 0.02 ns and the input C at 0.03 ns (each of them after the clock_rise_edge) . The problem is that each of them trigger the process and is changing the OUTPUT E but the output E cannot change so many times so fast and as a result i get a vital glitch.The final result is correct but does anyone know how can i avoid this vital glitch?

Can i make my design to check the input changes after i.e. 0.5ns so i can be sure that the output will change only once in every clock_period and not three times??

or are there any other solutions to fix this?

Thank you.

In my design i get some vital glitches and i think i know where do they come from.

Lets assume that i have a combinational circuit with INPUTS A,B,C and an OUTPUT E that depends from every input.These inputs are connected with flip flops but each flip flop is a part of a different component.

My problem is that the input A is changing i.e. at 0.01 ns ,the input B at 0.02 ns and the input C at 0.03 ns (each of them after the clock_rise_edge) . The problem is that each of them trigger the process and is changing the OUTPUT E but the output E cannot change so many times so fast and as a result i get a vital glitch.The final result is correct but does anyone know how can i avoid this vital glitch?

Can i make my design to check the input changes after i.e. 0.5ns so i can be sure that the output will change only once in every clock_period and not three times??

or are there any other solutions to fix this?

Thank you.