spade7

Newbie level 5

- Joined

- Jan 27, 2013

- Messages

- 8

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

- 1,356

Hello,

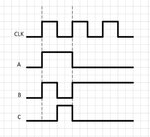

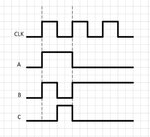

I am rather new on VHDL. I have done some code in the past but I have a problem concerning how to manipulate B and C signals (as shown below). Actually, it is a state machine and I am trying to change the logic of these signals (B & C) in half of the clock pulse. Could you please give me some hints how to do it? Thank you

I am rather new on VHDL. I have done some code in the past but I have a problem concerning how to manipulate B and C signals (as shown below). Actually, it is a state machine and I am trying to change the logic of these signals (B & C) in half of the clock pulse. Could you please give me some hints how to do it? Thank you