onion2014

Member level 1

- Joined

- Mar 25, 2013

- Messages

- 35

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,286

- Location

- NY

- Activity points

- 1,574

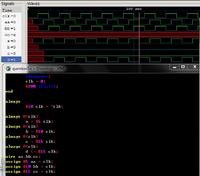

What is the difference between the following lines of code ?

reg1<= #10 reg2 ;

reg3 = # 10 reg4 ;

can anyone explain the difference, from the view of verilog event queue? Thanks.

reg1<= #10 reg2 ;

reg3 = # 10 reg4 ;

can anyone explain the difference, from the view of verilog event queue? Thanks.