strangesiva

Newbie level 6

- Joined

- Feb 12, 2012

- Messages

- 14

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

- 1,374

Hi ,

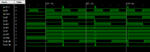

the below code uses dff for mod3 counter design . rst generated (using expression1) does not work,where as rst generated (using expression 2) works . what is the reason ?

the below code uses dff for mod3 counter design . rst generated (using expression1) does not work,where as rst generated (using expression 2) works . what is the reason ?

Code Verilog - [expand]

Last edited by a moderator: