jihrenee

Junior Member level 2

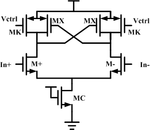

The image shown is a delay cell, where Vctrl is the control voltage. Where

MC: a current source work in triode region

MX: a negative resistance

MK: adjustable resistor

M+, M-: input pair

Connecting the delay cells in a loop will form a VCO.

Next, given Kvco, how can i size the MOS in this VCO to satisfy Kvco?

What i know so far is, i keep adjusting the size of MOS, run the simulation and draw the curve to calculate Kvco.

But strategy above is known as "hspice monkey" --- i'm just keep adjusting the size of MOS to ensure that the VCO will oscillate, and has enough swing.

Any direction to design a VCO?