EC.Engineer

Junior Member level 1

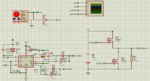

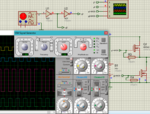

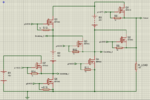

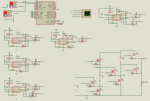

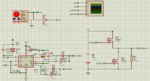

I am working on a multi-level invertor and using IR2110 for gate drive but I am facing a problem with the High side output. It does not seem to switch on. Please see the attached Proteus design for the basic test setup.

Is there anything I am missing in the connections? I am trying to follow the design given by @Tahmid on https://tahmidmc.blogspot.com/2013/01/using-high-low-side-driver-ir2110-with.html

Is there anything I am missing in the connections? I am trying to follow the design given by @Tahmid on https://tahmidmc.blogspot.com/2013/01/using-high-low-side-driver-ir2110-with.html