ishan.dalal

Newbie level 5

- Joined

- Mar 6, 2014

- Messages

- 10

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1

- Activity points

- 66

Hey Guys,

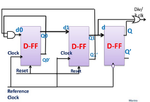

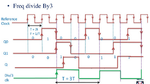

I am not able to grasp the waveforms of divide by 3 counter where two flip-flops produce waveforms at half frequency but at quadrature phase relation.

Could anyone please explain me waveforms?

Thanks in advance !

I am not able to grasp the waveforms of divide by 3 counter where two flip-flops produce waveforms at half frequency but at quadrature phase relation.

Could anyone please explain me waveforms?

Thanks in advance !