gavingt

Newbie

- Joined

- Dec 9, 2013

- Messages

- 3

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

- 1,350

You can see in the picture below the design our professor is having us implement. All the components simulate correctly and the design works perfectly on an FPGA board. But the testbench for the overall system is giving me tons of grief.

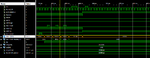

You can see in the picture below the design our professor is having us implement. All the components simulate correctly and the design works perfectly on an FPGA board. But the testbench for the overall system is giving me tons of grief. I'm getting this warning: Xst:2040 - Unit Microprocessor: 4 multi-source signals are replaced by logic (pull-up yes): A<0>, A<1>, A<2>, A<3>, but I don't know if that's a standard thing that Xilinx does or not. A(3:0) is the main bus going from the ROMs to the ALU.

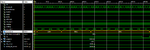

I'm just trying to pass values through the ALU right now. As you can see in attached waveform, it's replacing every '0' with 'U's, but leaving the '1's intact (compare Aluout and hex_input_display).

Oh, and in addition to the components pictured, I made a somewhat sloppy display decoder for displaying results and debouncing two of the push button inputs.

Here's the overall VHDL file:

Code VHDL - [expand]

Last edited by a moderator: